# UltraSPARC<sup>™</sup> User's Manual

# UltraSPARC-II UltraSPARC-II

**July 1997**

Sun Microelectronics 901 San Antonio Road Palo Alto, CA 94303

Part No: 802-7220-02

This July 1997 -02 Revision is only available online. The only changes made were to support hypertext links in the pdf file. Copyright © 1997 Sun Microsystems, Inc. All Rights Reserved.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED "AS IS" WITHOUT ANY EXPRESS REPRESENTATIONS OR WARRANTIES. IN ADDITION, SUN MICROSYSTEMS, INC. DISCLAIMS ALL IMPLIED REPRESENTATIONS AND WARRANTIES, INCLUDING ANY WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

This document contains proprietary information of Sun Microsystems, Inc. or under license from third parties. No part of this document may be reproduced in any form or by any means or transferred to any third party without the prior written consent of Sun Microsystems, Inc.

Sun, Sun Microsystems, and the Sun logo are trademarks or registered trademarks of Sun Microsystems, Inc. in the United States and other countries. All SPARC trademarks are used under license and are trademarks or registered trademarks of SPARC International, Inc. in the United States and other countries. Products bearing SPARC trademarks are based upon an architecture developed by Sun Microsystems, Inc.

The information contained in this document is not designed or intended for use in on-line control of aircraft, air traffic, aircraft navigation or aircraft communications; or in the design, construction, operation or maintenance of any nuclear facility. Sun disclaims any express or implied warranty of fitness for such uses.

Printed in the United States of America.

# **Contents**

|            | Pref  | ace                                  | 9  |

|------------|-------|--------------------------------------|----|

|            |       | Overview                             | 9  |

|            |       | A Brief History of SPARC             | 9  |

|            |       | How to Use This Book                 | 10 |

|            |       | Section $I$ — Introducing UltraSPARC |    |

| 1.         | Ultra | aSPARC Basics                        | 3  |

|            | 1.1   | Overview                             | 3  |

|            | 1.2   | Design Philosophy                    | 3  |

|            | 1.3   | Component Overview                   | 5  |

|            | 1.4   | UltraSPARC Subsystem                 | 10 |

| 2.         | Proc  | essor Pipeline                       | 11 |

|            | 2.1   | Introductions                        | 11 |

|            | 2.2   | Pipeline Stages                      | 12 |

| 3.         | Cacl  | ne Organization                      | 17 |

|            | 3.1   | Introduction                         | 17 |

| 4.         | Ove   | rview of the MMU                     | 21 |

|            | 4.1   | Introduction                         | 21 |

|            | 4.2   | Virtual Address Translation          | 21 |

|            |       | Section II — Going Deeper            |    |

| <b>5</b> . | Cacl  | ne and Memory Interactions           | 27 |

|            | 5.1   | Introduction                         | 27 |

#### UltraSPARC User's Manual

|    | 5.2   | Cache Flushing                                               | 27 |

|----|-------|--------------------------------------------------------------|----|

|    | 5.3   | Memory Accesses and Cacheability                             | 29 |

|    | 5.4   | Load Buffer                                                  | 39 |

|    | 5.5   | Store Buffer                                                 | 40 |

| 6. | MM    | U Internal Architecture                                      | 41 |

|    | 6.1   | Introduction                                                 | 41 |

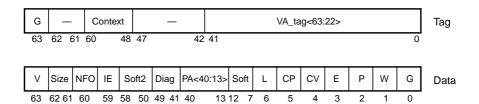

|    | 6.2   | Translation Table Entry (TTE)                                | 41 |

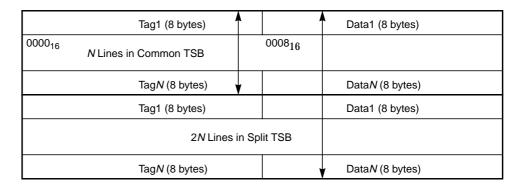

|    | 6.3   |                                                              | 44 |

|    | 6.4   | 9                                                            | 47 |

|    | 6.5   | MMU Operation Summary                                        | 50 |

|    | 6.6   | ASI Value, Context, and Endianness Selection for Translation | 52 |

|    | 6.7   | MMU Behavior During Reset, MMU Disable, and RED_state        | 54 |

|    | 6.8   | Compliance with the SPARC-V9 Annex F                         | 55 |

|    | 6.9   | MMU Internal Registers and ASI Operations                    | 55 |

|    | 6.10  | MMU Bypass Mode                                              | 68 |

|    | 6.11  | TLB Hardware                                                 | 69 |

| 7. | Ultra | SPARC External Interfaces                                    | 73 |

|    | 7.1   |                                                              | 73 |

|    | 7.2   |                                                              | 73 |

|    | 7.3   |                                                              | 76 |

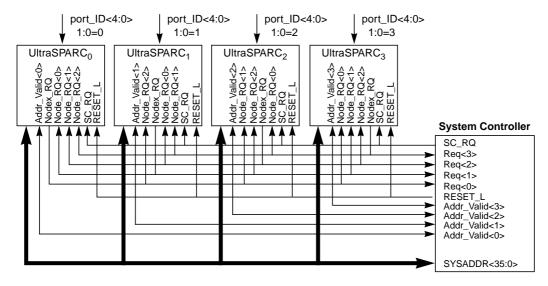

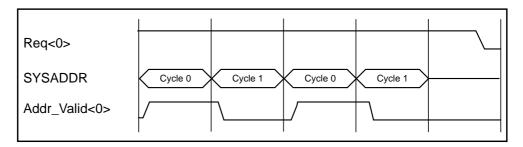

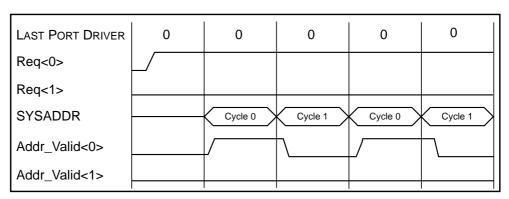

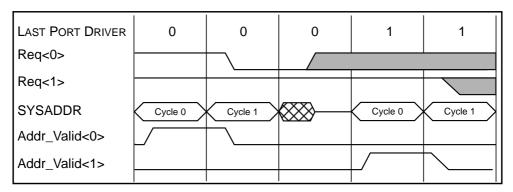

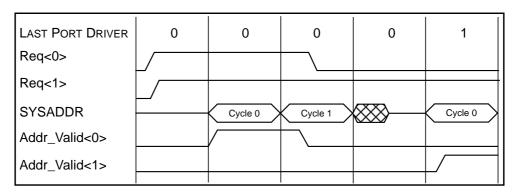

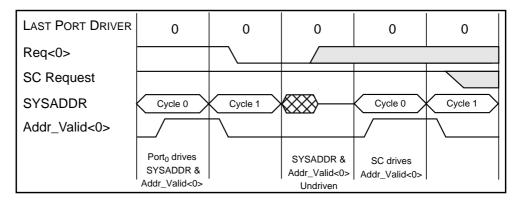

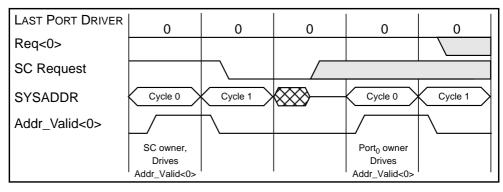

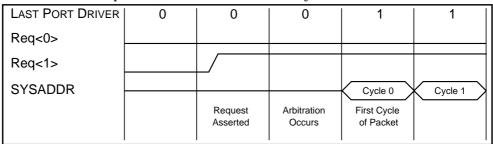

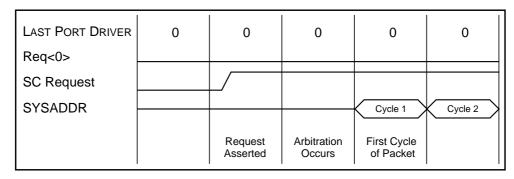

|    | 7.4   | SYSADDR Bus Arbitration Protocol                             | 84 |

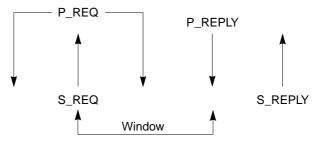

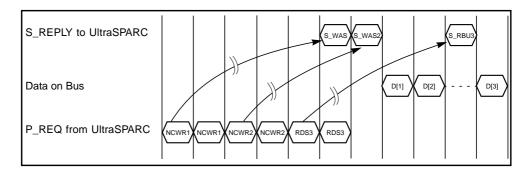

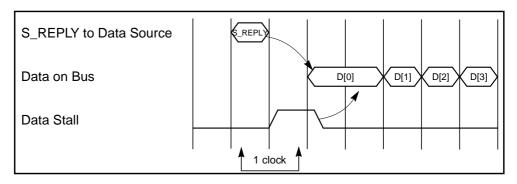

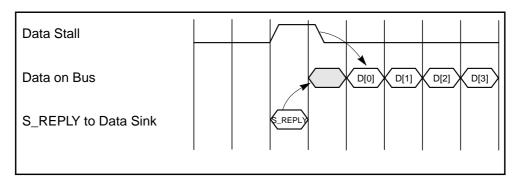

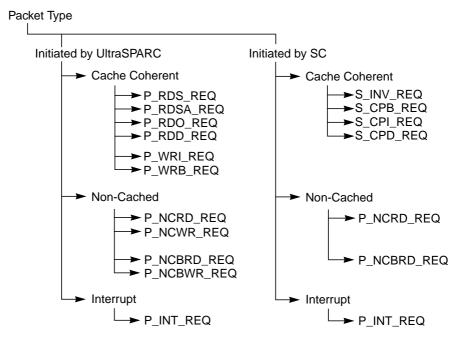

|    | 7.5   | UltraSPARC Interconnect Transaction Overview                 | 92 |

|    | 7.6   |                                                              | 94 |

|    | 7.7   | Cache Coherent Transactions                                  | 02 |

|    | 7.8   | Non-Cached Data Transactions                                 | 09 |

|    | 7.9   | S_RTO/S_ERR 1                                                | 11 |

|    | 7.10  | S_REQ                                                        | 11 |

|    | 7.11  | Writeback Issues                                             | 12 |

|    | 7.12  | Interrupts (P_INT_REQ)                                       | 16 |

|    | 7.13  | P_REPLY and S_REPLY 1                                        | 17 |

|    | 7.14  | Multiple Outstanding Transactions                            | 26 |

|    | 7.15  | Transaction Set Summary                                      | 29 |

|    | 7.16  | Transaction Sequences                                        | 31 |

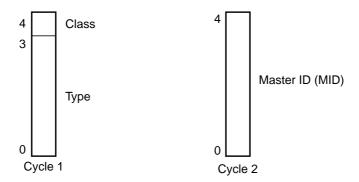

|    | 7.17  | Interconnect Packet Formats                                  | 38 |

|    | 7.18  | WriteInvalidate                                              | 43 |

| 8. | Addı  | ress Spaces, ASIs, ASRs, and Traps                           | 45 |

|    | 8.1   |                                                              | 45 |

|    | 8.2   | Physical Address Space                                       | 45 |

|    | 83    | Alternate Address Spaces                                     | 46 |

|     | 8.4   | Ancillary State Registers                                | 156 |

|-----|-------|----------------------------------------------------------|-----|

|     | 8.5   | Other UltraSPARC Registers                               | 158 |

|     | 8.6   | Supported Traps                                          | 158 |

| 9.  | Inter | rupt Handling                                            | 161 |

|     | 9.1   | Interrupt Vectors                                        | 161 |

|     | 9.2   | Interrupt Global Registers                               | 163 |

|     | 9.3   | Interrupt ASI Registers                                  | 163 |

|     | 9.4   | Software Interrupt (SOFTINT) Register                    | 166 |

| 10  | Rese  | t and RED_state                                          | 169 |

| -0. | 10.1  | Overview                                                 | 169 |

|     | 10.2  | RED_state Trap Vector                                    | 171 |

|     | 10.3  | Machine State after Reset and in RED_state               | 171 |

| 11  | ъ     |                                                          |     |

| 11. |       | Handling                                                 | 175 |

|     | 11.1  | Overview                                                 | 175 |

|     | 11.2  | Memory Errors                                            | 178 |

|     | 11.3  | Memory Error Registers                                   | 179 |

|     | 11.4  | UltraSPARC Data Buffer (UDB) Control Register            | 185 |

|     | 11.5  | Overwrite Policy                                         | 185 |

| 12. | Instr | Section III — UltraSPARC and SPARC-V9 uction Set Summary | 189 |

|     |       | SPARC Extended Instructions                              | 195 |

| 13. | 13.1  | Introduction                                             | 195 |

|     | 13.1  | SHUTDOWN                                                 | 195 |

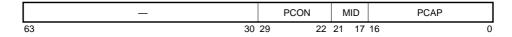

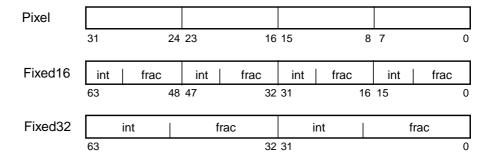

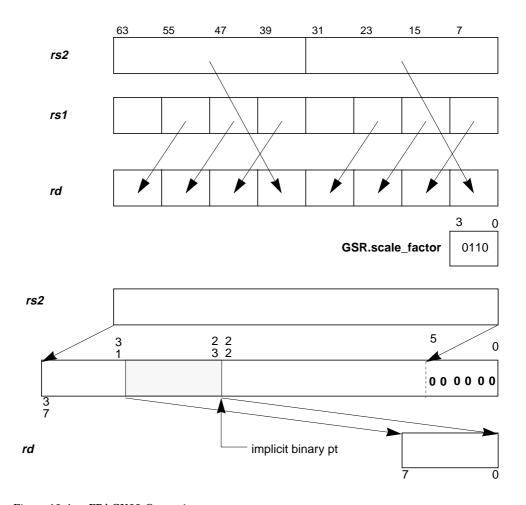

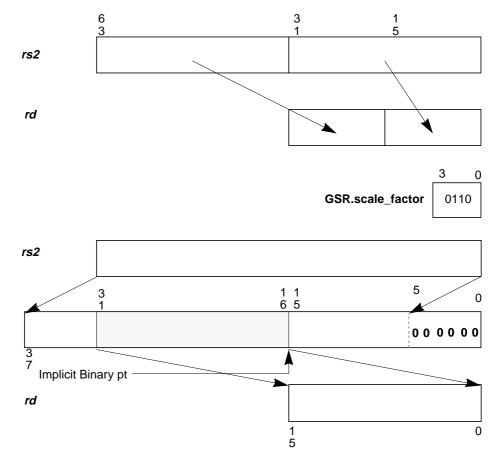

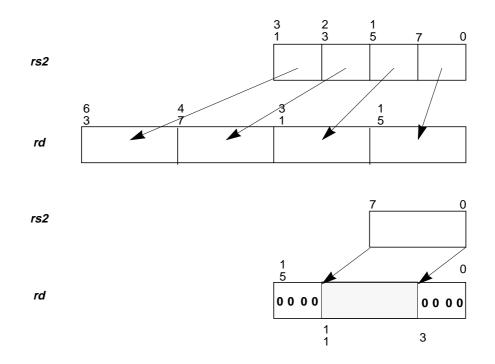

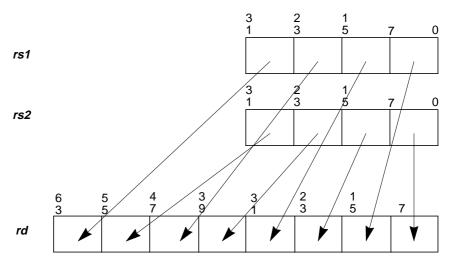

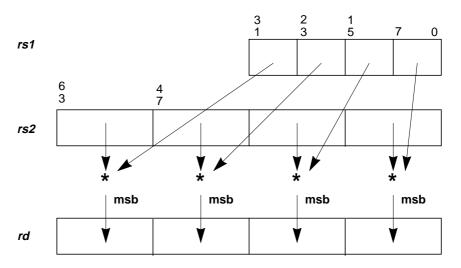

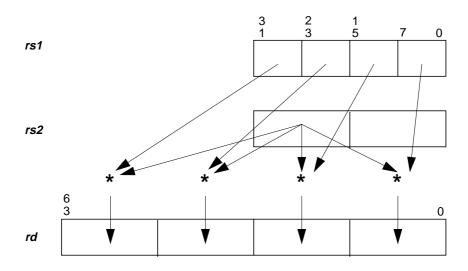

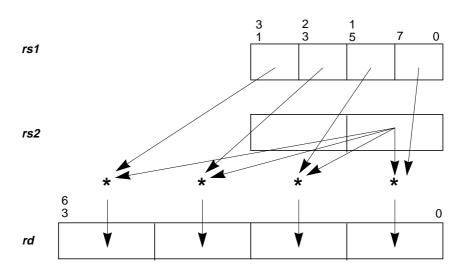

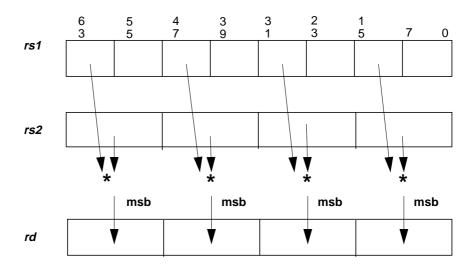

|     | 13.3  | Graphics Data Formats                                    | 196 |

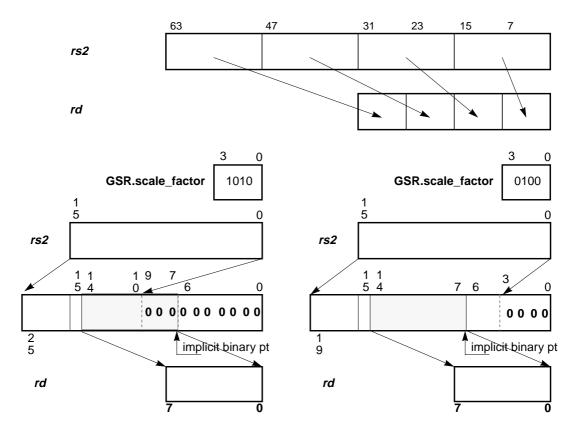

|     | 13.4  | Graphics Status Register (GSR)                           | 197 |

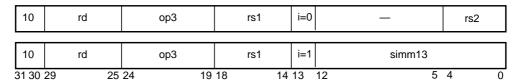

|     | 13.5  | Graphics Instructions                                    | 198 |

|     | 13.6  | Memory Access Instructions                               | 225 |

| 11  | Imnl  | ementation Dependencies                                  | 235 |

| 14. |       | SPARC-V9 General Information                             | 235 |

|     | 14.1  | SPARC-V9 Integer Operations                              | 240 |

|     | 14.2  | SPARC-V9 Floating-Point Operations                       | 242 |

|     | 14.3  | SPARC-V9 Memory-Related Operations                       | 247 |

|     | 14.5  | Non-SPARC-V9 Extensions                                  | 249 |

| 15  |       |                                                          |     |

| 10. | SPAI  | RC-V9 Memory Models                                      | 255 |

|     | 15.1  | Overview                                                 | 255 |

|     | 15.2  | Supported Memory Models                    | 256 |

|-----|-------|--------------------------------------------|-----|

|     |       | Section IV — Producing Optimized Code      |     |

| 16. | Code  | Generation Guidelines                      | 261 |

|     | 16.1  |                                            | 261 |

|     | 16.2  | Instruction Stream Issues                  | 261 |

|     | 16.3  | Data Stream Issues                         | 272 |

| 17. | Grou  | ping Rules and Stalls                      | 281 |

|     | 17.1  | Introduction                               | 281 |

|     | 17.2  | General Grouping Rules                     | 282 |

|     | 17.3  | Instruction Availability                   | 283 |

|     | 17.4  | Single Group Instructions                  | 283 |

|     | 17.5  | Integer Execution Unit (IEU) Instructions  | 284 |

|     | 17.6  | Control Transfer Instructions              | 287 |

|     | 17.7  | Load / Store Instructions                  | 290 |

|     | 17.8  | Floating-Point and Graphic Instructions    | 295 |

|     |       |                                            |     |

|     |       | Appendixes                                 |     |

| A.  | Debu  | ıg and Diagnostics Support                 | 303 |

|     | A.1   | Overview                                   | 303 |

|     | A.2   | Diagnostics Control and Accesses           | 303 |

|     | A.3   | Dispatch Control Register                  | 303 |

|     | A.4   | Floating-Point Control                     | 304 |

|     | A.5   | Watchpoint Support                         | 304 |

|     | A.6   | LSU_Control_Register                       | 306 |

|     | A.7   | I-Cache Diagnostic Accesses                | 309 |

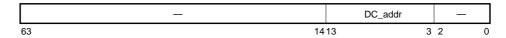

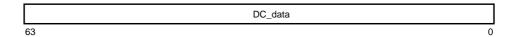

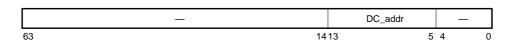

|     | A.8   | D-Cache Diagnostic Accesses                | 314 |

|     | A.9   | E-Cache Diagnostics Accesses               | 315 |

| В.  | Perfo | ormance Instrumentation                    | 319 |

|     | B.1   | Overview                                   | 319 |

|     | B.2   | Performance Control and Counters           | 319 |

|     | B.3   | PCR/PIC Accesses                           | 321 |

|     | B.4   | Performance Instrumentation Counter Events | 321 |

| C.  | Pow   | er Management                              | 327 |

|     | C.1   | Overview                                   | 327 |

|     | C.2   | Power-Down Mode                            | 327 |

|    | C.3   | Power-Up                                 | 328 |

|----|-------|------------------------------------------|-----|

| D. | IEEE  | 1149.1 Scan Interface                    | 329 |

|    | D.1   | Introduction                             | 329 |

|    | D.2   | Interface                                | 329 |

|    | D.3   | Test Access Port (TAP) Controller        | 330 |

|    | D.4   | Instruction Register                     | 333 |

|    | D.5   | Instructions                             | 333 |

|    | D.6   | Public Test Data Registers               | 335 |

| E. | Pin a | and Signal Descriptions                  | 337 |

|    | E.1   | Introduction                             | 337 |

|    | E.2   | Pin Descriptions                         | 337 |

|    | E.3   | Signal Descriptions                      | 341 |

| F. | ASI   | Names                                    | 345 |

|    | F.1   | Introduction                             | 345 |

| G. | Diffe | erences Between UltraSPARC Models        | 351 |

|    | G.1   | Introduction                             | 351 |

|    | G.2   | Summary                                  | 351 |

|    | G.3   | References to Model-Specific Information | 352 |

|    |       | Back Matter                              |     |

|    | Glos  | sary                                     | 357 |

|    | Bibli | iography                                 | 363 |

|    |       | General References                       | 363 |

|    |       | Sun Microelectronics (SME) Publications  | 364 |

|    |       | How to Contact SME                       | 365 |

|    |       | On Line Resources                        | 365 |

|    | Inde  | x                                        | 367 |

UltraSPARC User's Manual

# Preface

#### **Overview**

Welcome to the *UltraSPARC User's Manual*. This book contains information about the architecture and programming of UltraSPARC™, Sun Microsystems' family of SPARC-V9-compliant processors. It describes the UltraSPARC-I and UltraSPARC-II processor implementasions.

This book contains information on:

- The UltraSPARC system architecture

- The components that make up an UltraSPARC processor

- Memory and low-level system management, including detailed information needed by operating system programmers

- Extensions to and implementation-dependencies of the SPARC-V9 architecture

- Techniques for managing the pipeline and for producing optimized code

# A Brief History of SPARC

SPARC stands for Scalable Processor ARChitecture, which was first announced in 1987. Unlike more traditional processor architectures, SPARC is an open standard, freely available through license from SPARC International, Inc. Any company that obtains a license can manufacture and sell a SPARC-compliant processor.

By the early 1990s SPARC processors we available from over a dozen different vendors, and over 8,000 SPARC-compliant applications had been certified.

In 1994, SPARC International, Inc. published *The SPARC Architecture Manual, Version 9*, which defined a powerful 64-bit enhancement to the SPARC architecture. SPARC-V9 provided support for:

- 64-bit virtual addresses and 64-bit integer data

- Fault tolerance

- Fast trap handling and context switching

- Big- and little-endian byte orders

UltraSPARC is the first family of SPARC-V9-compliant processors available from Sun Microsystems, Inc.

#### How to Use This Book

This book is a companion to *The SPARC Architecture Manual, Version 9*, which is available from many technical bookstores or directly from its copyright holder:

SPARC International, Inc. 535 Middlefield Road, Suite 210 Menlo Park, CA 94025 (415) 321-8692

The SPARC Architecture Manual, Version 9 provides a complete description of the SPARC-V9 architecture. Since SPARC-V9 is an open architecture, many of the implementation decisions have been left to the manufacturers of SPARC-compliant processors. These "implementation dependencies" are introduced in *The SPARC Architecture Manual, Version 9*; they are numbered throughout the body of the text, and are cross referenced in Appendix C that book.

This book, the *UltraSPARC User's Manual*, describes the UltraSPARC-I and UltraSPARC-II implementations of the SPARC-V9 architecture. It provides specific information about UltraSPARC processors, including how each SPARC-V9 implementation dependency was resolved. (See Chapter 14, "Implementation Dependencies," for specific information.) This manual also describes extensions to SPARC-V9 that are available (currently) only on UltraSPARC processors.

A great deal of background information and a number of architectural concepts are not contained in this book. You will find cross references to *The SPARC Architecture Manual, Version 9* located throughout this book. You should have a copy of that book at hand whenever you are working with the *UltraSPARC User's Manual*. For detailed information about the electrical and mechanical characteristics of the processor, including pin and pad assignments, consult the *UltraSPARC-I Data Sheet*. The "Bibliography" on page 363 describes how to obtain the data sheet.

#### Textual Conventions

This book uses the same textual conventions as *The SPARC Architecture Manual, Version 9.* They are summarized here for convenience.

Fonts are used as follows:

- Italic font is used for register names, instruction fields, and read-only register fields.

- Typewriter font is used for literals and software examples.

- **Bold** font is used for emphasis.

- UPPER CASE items are acronyms, instruction names, or writable register fields.

- *Italic sans serif* font is used for exception and trap names.

- Underbar characters (\_) join words in register, register field, exception, and trap names. Such words can be split across lines at the underbar without an intervening hyphen.

The following notational conventions are used:

- Square brackets '[]' indicate a numbered register in a register file.

- Angle brackets '< >' indicate a bit number or colon-separated range of bit numbers within a field.

- Curly braces '{ }' are used to indicate textual substitution.

- The  $\square$  symbol designates concatenation of bit vectors. A comma ',' on the left side of an assignment separates quantities that are concatenated for the purpose of assignment.

#### **Contents**

This manual has the following organization.

Section I, "Introducing UltraSPARC," presents an overview of the UltraSPARC architecture. Section I contains the following chapters:

- Chapter 1, "UltraSPARC Basics," describes the architecture in general terms and introduces its components.

- Chapter 2, "Processor Pipeline," describes UltraSPARC's 9-stage pipeline.

- Chapter 3, "Cache Organization," describes the UltraSPARC caches.

Chapter 4, "Overview of the MMU, " describes the UltraSPARC MMU, its architecture, how it performs virtual address translation, and how it is programmed.

Section II, "Going Deeper," presents detailed information about UltraSPARC architecture and programming. Section II contains the following chapters:

- Chapter 5, "Cache and Memory Interactions," describes cache coherency and cache flushing.

- Chapter 6, "MMU Internal Architecture," describes in detail the internal architecture of the MMU and how to program it.

- Chapter 7, "UltraSPARC External Interfaces," describes in detail the external transactions that UltraSPARC performs, including interactions with the caches and the SYSADDR bus, and interrupts.

- Chapter 8, "Address Spaces, ASIs, ASRs, and Traps," describes the address spaces that UltraSPARC supports, and how it handles traps.

- Chapter 9, "Interrupt Handling," describes how UltraSPARC processes interrupts.

- Chapter 10, "Reset and RED\_state," describes how UltraSPARC handles the various SPARC-V9 reset conditions, and how it implements RED\_state.

- Chapter 11, "Error Handling," discusses how UltraSPARC handles system errors and describes the available error status registers.

Section III, "UltraSPARC and SPARC-V9," describes UltraSPARC as an implementation of the SPARC-V9 architecture. Section III contains the following chapters:

- Chapter 12, "Instruction Set Summary," lists all supported instructions, including both SPARC-V9 core instructions and UltraSPARC extended instructions.

- Chapter 13, "UltraSPARC Extended Instructions," contains detailed documentation of the extended instructions that UltraSPARC has added to the SPARC-V9 instruction set.

- Chapter 14, "Implementation Dependencies," discusses how UltraSPARC has resolved each of the implementation-dependencies defined by the SPARC-V9 architecture.

• Chapter 15, "SPARC-V9 Memory Models," describes the supported memory models (which are documented fully in *The SPARC Architecture Manual, Version 9*). Low-level programmers and operating system implementors should study this chapter to understand how their code will interact with the UltraSPARC cache and memory systems.

Section IV, "Producing Optimized Code," contains detailed information for assembly language programmers and compiler developers. Section IV contains the following chapters:

- Chapter 16, "Code Generation Guidelines," contains detailed information about generating optimum UltraSPARC code.

- Chapter 17, "Grouping Rules and Stalls," describes instruction interdependencies and optimal instruction ordering.

Appendixes contain low-level technical material or information not needed for a general understanding of the architecture. The manual contains the following appendixes:

- Appendix A, "Debug and Diagnostics Support," describes diagnostics registers and capabilities.

- Appendix B, "Performance Instrumentation," describes built-in capabilities to measure UltraSPARC performance.

- Appendix C, "Power Management," describes UltraSPARC's Energy Star compliant power-down mode.

- Appendix D, "IEEE 1149.1 Scan Interface," contains information about the scan interface for UltraSPARC.

- Appendix E, "Pin and Signal Descriptions," contains general information about the pins and signals of the UltraSPARC and its components.

- Appendix F, "ASI Names," contains an alphabetical listing of the names and suggested macro syntax for all supported ASIs.

A Glossary, Bibliography, and Index complete the book.

UltraSPARC User's Manual

# $Section I-Introducing \ Ultra SPARC$

| 1. | UltraSPARC Basics   | 3  |

|----|---------------------|----|

| 2. | Processor Pipeline  | 11 |

| 3. | Cache Organization  | 17 |

| 4  | Overview of the MMU | 21 |

UltraSPARC User's Manual

#### 1.1 Overview

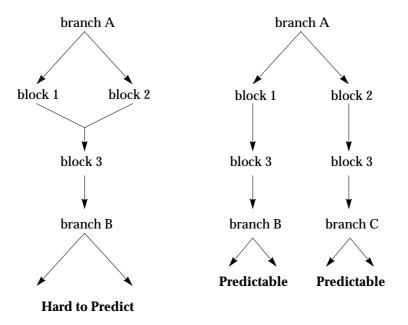

UltraSPARC is a high-performance, highly integrated superscalar processor implementing the 64-bit SPARC-V9 RISC architecture. UltraSPARC is capable of *sustaining* the execution of up to *four* instructions per cycle, even in the presence of conditional branches and cache misses. This is due mainly to the asynchronous aspect of the units feeding instructions and data to the rest of the pipeline. Instructions predicted to be executed are issued in program order to multiple functional units, execute in parallel and, for added parallelism, can complete out-of-order. In order to further increase the number of instructions executed per cycle (IPC), instructions from two basic blocks (that is, instructions before and after a conditional branch) can be issued in the same group.

UltraSPARC is a full implementation of the 64-bit SPARC-V9 architecture. It supports a 44-bit virtual address space and a 41-bit physical address space. The core instruction set has been extended to include graphics instructions that provide the most common operations related to two-dimensional image processing, two-and three-dimensional graphics and image compression algorithms, and parallel operations on pixel data with 8- and 16-bit components. Support for high bandwidth **bcopy** is also provided through block load and block store instructions.

# 1.2 Design Philosophy

The execution time of an application is the product of three factors: the number of instructions generated by the compiler, the average number of cycles required per instruction, and the cycle time of the processor. The architecture and implementation of UltraSPARC, coupled with new compiler techniques, makes it possible to reduce each component while not deteriorating the other two.

The number of instructions for a given task depends on the instruction set and on compiler optimizations (dead code elimination, constant propagation, profiling for code motion, and so on). Since it is based on the SPARC-V9 architecture, UltraSPARC offers features that can help reduce the total instruction count:

- 64-bit integer processing

- Additional floating-point registers (beyond the number offered in SPARC-V8), which can be used to eliminate floating-point loads and stores

- Enhanced trap model with alternate global registers

The average number of cycles per instruction (CPI) depends on the architecture of the processor and on the ability of the compiler to take advantage of the hardware features offered. The UltraSPARC execution units (ALUs, LD/ST, branch, two floating-point, and two graphics) allow the CPI to be as low as 0.25 (four instructions per cycle). To support this high execution bandwidth, sophisticated hardware is provided to supply:

- 1. Up to four instructions per cycle, even in the presence of conditional branches

- 2. Data at a rate of 16 bytes-per-cycle from the external cache to the data cache, or 8 bytes-per-cycle into the register files.

To reduce instruction dependency stalls, UltraSPARC has short latency operations and provides direct bypassing between units or within the same unit. The impact of cache misses, usually a large contributor to the CPI, is reduced significantly through the use of de-coupled units (prefetch unit, load buffer, and store buffer), which operate asynchronously with the rest of the pipeline.

Other features such as a fully pipelined interface to the external cache (E-Cache) and support for speculative loads, coupled with sophisticated compiler techniques such as software pipelining and cross-block scheduling also reduce the CPI significantly.

A balanced architecture must be able to provide a low CPI without affecting the cycle time. Several of UltraSPARC's architectural features, coupled with an aggressive implementation and state-of-the-art technology, have made it possible to achieve a short cycle time (see Table 1-1). The pipeline is organized so that large scalarity (four), short latencies, and multiple bypasses do not affect the cycle time significantly.

Table 1-1 Implementation Technologies and Cycle Times

|            | UltraSPARC-I    | UltraSPARC-II   |

|------------|-----------------|-----------------|

| Technology | 0.5 μ CMOS      | 0.35 μ CMOS     |

| Cycle Time | 7 ns and faster | 4 ns and faster |

# 1.3 Component Overview

Figure 1-1 shows a block diagram of the UltraSPARC processor.

Figure 1-1 UltraSPARC Block Diagram

The block diagram illustrates the following components:

- Prefetch and Dispatch Unit (PDU), including logic for branch prediction

- 16Kb Instruction Cache (I-Cache)

- Memory Management Unit (MMU), containing a 64-entry Instruction Translation Lookaside Buffer (iTLB) and a 64-entry Data Translation Lookaside Buffer (dTLB)

- Integer Execution Unit (IEU) with two Arithmetic and Logic Units (ALUs)

- Load/Store Unit (LSU) with a separate address generation adder

- Load buffer and store buffer, decoupling data accesses from the pipeline

- A 16Kb Data Cache (D-Cache)

- Floating-Point Unit (FPU) with independent add, multiply, and divide/square root sub-units

- Graphics Unit (GRU) with two independent execution pipelines

- External Cache Unit (ECU), controlling accesses to the External Cache (E-Cache)

- Memory Interface Unit (MIU), controlling accesses to main memory and I/O space

# 1.3.1 Prefetch and Dispatch Unit (PDU)

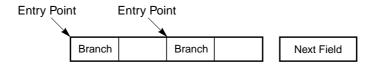

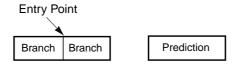

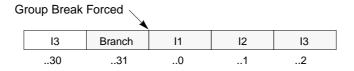

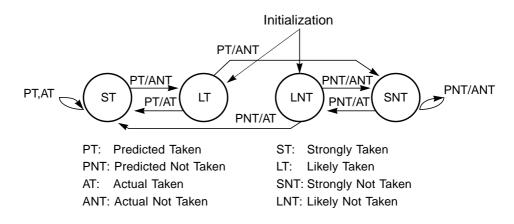

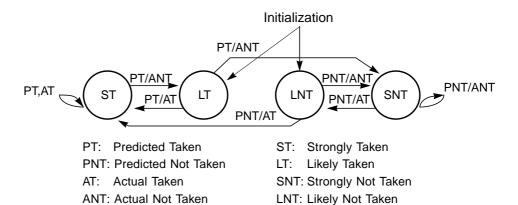

The prefetch and dispatch unit fetches instructions before they are actually needed in the pipeline, so the execution units do not starve for instructions. Instructions can be prefetched from all levels of the memory hierarchy; that is, from the instruction cache, the external cache, and main memory. In order to prefetch across conditional branches, a dynamic branch prediction scheme is implemented in hardware. The outcome of a branch is based on a two-bit history of the branch. A "next field" associated with every four instructions in the instruction cache (I-Cache) points to the next I-Cache line to be fetched. The use of the next field makes it possible to follow taken branches and to provide nearly the same instruction bandwidth achieved while running sequential code. Prefetched instructions are stored in the Instruction Buffer until they are sent to the rest of the pipeline; up to 12 instructions can be buffered.

## 1.3.2 Instruction Cache (I-Cache)

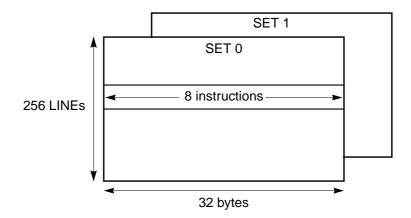

The instruction cache is a 16 Kbyte two-way set associative cache with 32 byte blocks. The cache is physically indexed and contains physical tags. The set is predicted as part of the "next field;" thus, only the index bits of an address (13 bits, which matches the minimum page size) are needed to address the cache. The I-Cache returns up to 4 instructions from an 8-instruction-wide cache line.

# 1.3.3 Integer Execution Unit (IEU)

The IEU contains the following components:

- Two ALUs

- A multi-cycle integer multiplier

- A multi-cycle integer divider

- Eight register windows

- Four sets of global registers (normal, alternate, MMU, and interrupt globals)

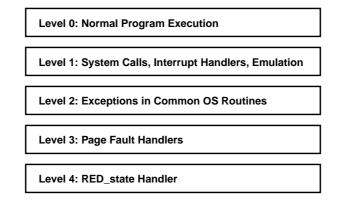

- The trap registers (See Table 1-2 for supported trap levels)

Table 1-2 Supported Trap Levels

|             | UltraSPARC-I | UltraSPARC-II |

|-------------|--------------|---------------|

| MAXTL       | 4            | 4             |

| Trap Levels | 5            | 5             |

# 1.3.4 Floating-Point Unit (FPU)

The FPU is partitioned into separate execution units, which allows the UltraSPARC processor to issue and execute two floating-point instructions per cycle. Source and result data are stored in the 32-entry register file, where each entry can contain a 32-bit value or a 64-bit value. Most instructions are fully pipelined, (with a throughput of one per cycle), have a latency of three, and are not affected by the precision of the operands (same latency for single- or double-precision). The divide and square root instructions are not pipelined and take 12/22 cycles (single/double) to execute but they do not stall the processor. Other instructions, following the divide/square root can be issued, executed, and retired to the register file before the divide/square root finishes. A precise exception model is maintained by synchronizing the floating-point pipe with the integer pipe and by predicting traps for long latency operations. See Section 7.3.1, "Precise Traps," in *The SPARC Architecture Manual, Version 9*.

# 1.3.5 Graphics Unit (GRU)

UltraSPARC introduces a comprehensive set of graphics instructions that provide fast hardware support for two-dimensional and three-dimensional image and video processing, image compression, audio processing, etc. 16-bit and 32-bit partitioned add, boolean, and compare are provided. 8-bit and 16-bit partitioned multiplies are supported. Single cycle pixel distance, data alignment, packing, and merge operations are all supported in the GRU.

# 1.3.6 Memory Management Unit (MMU)

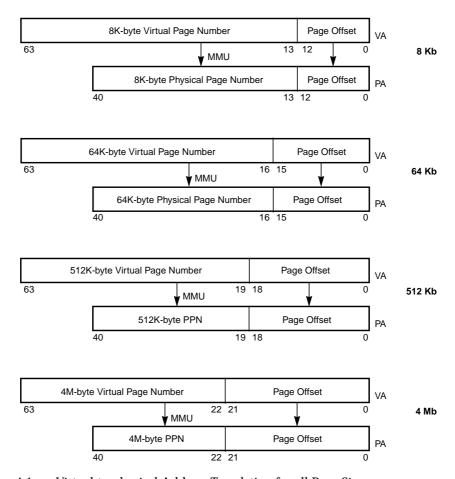

The MMU provides mapping between a 44-bit virtual address and a 41-bit physical address. This is accomplished through a 64-entry iTLB for instructions and a 64-entry dTLB for data; both TLBs are fully associative. UltraSPARC provides hardware support for a software-based TLB miss strategy. A separate set of global registers is available to process MMU traps. Page sizes of 8Kb (13-bit offset), 64Kb (16-bit offset), 512Kb (19-bit offset), and 4Mb (22-bit offset) are supported.

### 1.3.7 Load/Store Unit (LSU)

The LSU is responsible for generating the virtual address of all loads and stores (including atomics and ASI loads), for accessing the D-Cache, for decoupling load misses from the pipeline through the Load Buffer, and for decoupling stores through the Store Buffer. One load or one store can be issued per cycle.

## 1.3.8 Data Cache (D-Cache)

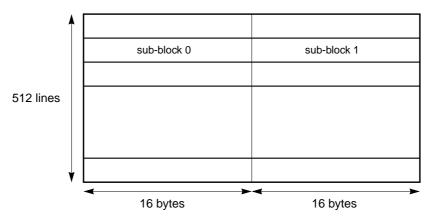

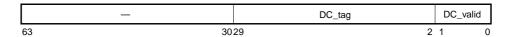

The D-Cache is a write-through, non-allocating, 16Kb direct-mapped cache with two 16-byte sub-blocks per line. It is virtually indexed and physically tagged (VIPT). The tag array is dual ported, so tag updates due to line fills do not collide with tag reads for incoming loads. Snoops to the D-Cache use the second tag port, so they do not delay incoming loads.

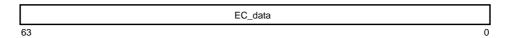

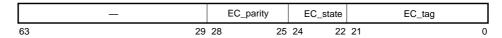

# 1.3.9 External Cache Unit (ECU)

The main role of the ECU is to handle I-Cache and D-Cache misses efficiently. The ECU can handle one access per cycle to the External Cache (E-Cache). Accesses to the E-Cache are pipelined, which effectively makes the E-Cache part of the instruction pipeline. Programs with large data sets can keep data in the E-Cache and can schedule instructions with load latencies based on E-Cache latency. Floating-point code can use this feature to effectively hide D-Cache misses.

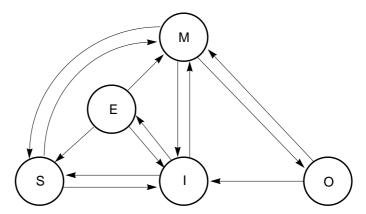

Table 1-5 on page 10 shows the E-Cache sizes that each UltraSPARC model supports. Regardless of model, however, the E-Cache line size is always 64 bytes. UltraSPARC uses a MOESI (Modified, Own, Exclusive, Shared, Invalid) protocol to maintain coherence across the system.

| Table 1-3 | Supported | E-Cache | Sizes |

|-----------|-----------|---------|-------|

|-----------|-----------|---------|-------|

| E-Cache Size | UltraSPARC-I | UltraSPARC-II |

|--------------|--------------|---------------|

| 512 Kb       | ✓            | ✓             |

| 1 Mb         | ✓            | ✓             |

| 2 Mb         | ✓            | ✓             |

| 4 Mb         | ✓            | ✓             |

| 8 Mb         |              | ✓             |

| 16 Mb        |              | 1             |

The ECU provides overlap processing during load and store misses. For instance, stores that hit the E-Cache can proceed while a load miss is being processed. The ECU can process reads and writes indiscriminately, without a costly turn-around penalty (only 2 cycles). Finally, the ECU handles snoops.

Block loads and block stores, which load/store a 64-byte line of data from memory to the floating-point register file, are also processed efficiently by the ECU, providing high transfer bandwidth without polluting the E-Cache.

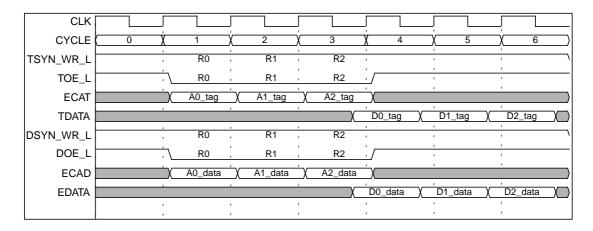

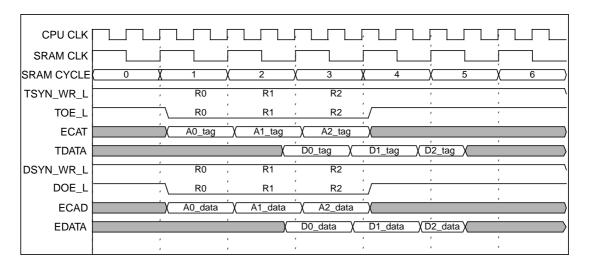

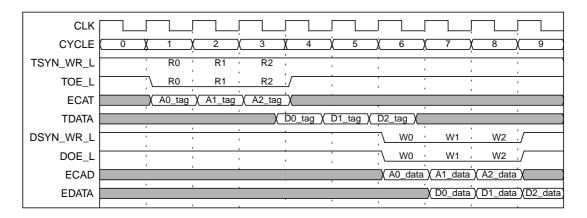

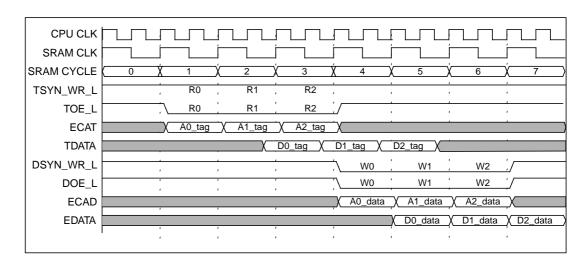

#### 1.3.9.1 E-Cache SRAM Modes

Different UltraSPARC models support various E-Cache SRAM configurations using one or more SRAM "modes." Table 1-5 shows the modes that each UltraSPARC model supports. The modes are described below.

Table 1-4 Supported E-Cache SRAM Modes

| SRAM Mode | UltraSPARC-I | UltraSPARC-II |

|-----------|--------------|---------------|

| 1-1-1     | ✓            | ✓             |

| 2-2       |              | 1             |

#### 1-1-1 (Pipelined) Mode:

The E-Cache SRAMS have a cycle time equal to the processor cycle time. The name "1–1–1" indicates that it takes one processor clock to send the address, one to access the SRAM array, and one to return the E-Cache data. 1–1–1 mode has a 3 cycle pin-to-pin latency and provides the best possible E-Cache throughput.

#### 2-2 (Register-Latched) Mode:

The E-Cache SRAMS have a cycle time equal to one-half the processor cycle time. The name "2–2" indicates that it takes two processor clocks to send the address and two clocks to access and return the E-Cache data. 2–2 mode has a 4 cycle pinto-pin latency, which provides lower E-Cache throughput at reduced cost.

# 1.3.10 Memory Interface Unit (MIU)

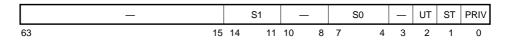

The MIU handles all transactions to the system controller; for example, external cache misses, interrupts, snoops, writebacks, and so on. The MIU communicates with the system at some model-dependent fraction of the UltraSPARC frequency. Table 1-5 shows the possible ratios between the processor and system clock frequencies for each UltraSPARC model.

| Frequency Ratio | UltraSPARC-I | UltraSPARC-II |

|-----------------|--------------|---------------|

| 2:1             | ✓            | ✓             |

| 3:1             | ✓            | 1             |

| 1.1             |              | ./            |

Table 1-5 Model-Dependent Processor : System Clock Frequency Ratios

# 1.4 UltraSPARC Subsystem

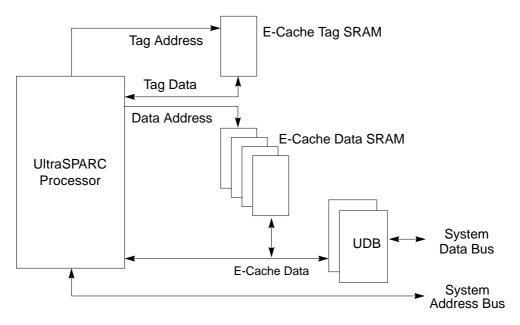

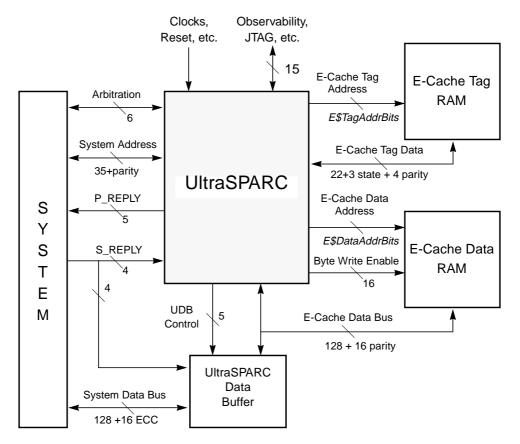

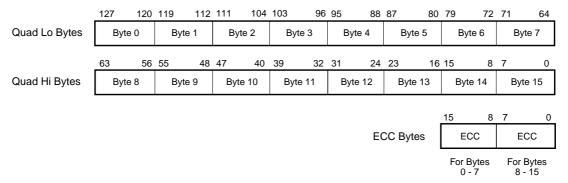

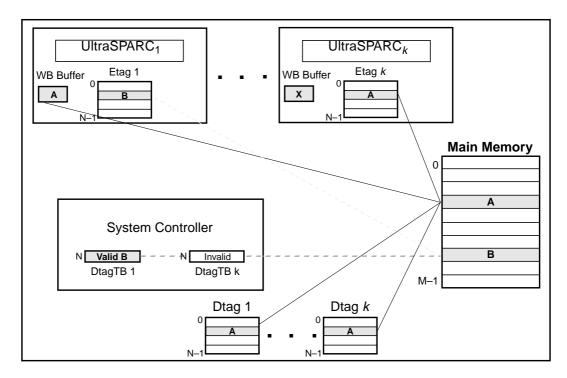

Figure 1-2 shows a complete UltraSPARC subsystem, which consists of the UltraSPARC processor, synchronous SRAM components for the E-Cache tags and data, and two UltraSPARC Data Buffer (UDB) chips. The UDBs isolate the E-Cache from the system, provide data buffers for incoming and outgoing system transactions, and provide ECC generation and checking.

Figure 1-2 UltraSPARC Subsystem

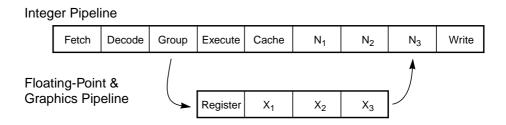

#### 2.1 Introductions

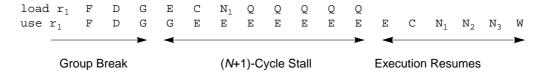

UltraSPARC contains a 9-stage pipeline. Most instructions go through the pipeline in exactly 9 stages. The instructions are considered terminated after they go through the last stage (W), after which changes to the processor state are irreversible. Figure 2-1 shows a simplified diagram of the integer and floating-point pipeline stages.

Figure 2-1 UltraSPARC Pipeline Stages (Simplified)

Three additional stages are added to the integer pipeline to make it symmetrical with the floating-point pipeline. This simplifies pipeline synchronization and exception handling. It also eliminates the need to implement a floating-point queue.

Floating-point instructions with a latency greater than three (divide, square root, and inverse square root) behave differently than other instructions; the pipe is "extended" when the instruction reaches stage  $N_1$ . See Chapter 16, "Code Generation Guidelines" for more information. Memory operations are allowed to proceed asynchronously with the pipeline in order to support latencies longer than the latency of the on-chip D-Cache.

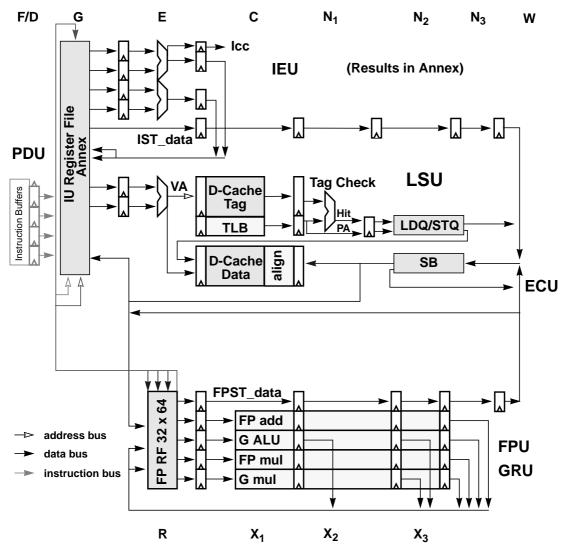

# 2.2 Pipeline Stages

This section describes each pipeline stage in detail. Figure 2-2 illustrates the pipeline stages.

Figure 2-2 UltraSPARC Pipeline Stages (Detail)

## 2.2.1 Stage 1: Fetch (F) Stage

Prior to their execution, instructions are fetched from the Instruction Cache (I-Cache) and placed in the Instruction Buffer, where eventually they will be selected to be executed. Accessing the I-Cache is done during the F Stage. Up to four instructions are fetched along with branch prediction information, the predicted target address of a branch, and the predicted set of the target. The high bandwidth provided by the I-Cache (4 instructions/cycle) allows UltraSPARC to prefetch instructions ahead of time based on the current instruction flow and on branch prediction. Providing a fetch bandwidth greater than or equal to the maximum execution bandwidth assures that, for well behaved code, the processor does not starve for instructions. Exceptions to this rule occur when branches are hard to predict, when branches are very close to each other, or when the I-Cache miss rate is high.

# 2.2.2 Stage 2: Decode (D) Stage

After being fetched, instructions are pre-decoded and then sent to the Instruction Buffer. The pre-decoded bits generated during this stage accompany the instructions during their stay in the Instruction Buffer. Upon reaching the next stage (where the grouping logic lives) these bits speed up the parallel decoding of up to 4 instructions.

While it is being filled, the Instruction Buffer also presents up to 4 instructions to the next stage. A pair of pointers manage the Instruction Buffer, ensuring that as many instructions as possible are presented *in order* to the next stage.

# 2.2.3 Stage 3: Grouping (G) Stage

The G Stage logic's main task is to group and dispatch a maximum of four valid instructions in one cycle. It receives a maximum of four valid instructions from the Prefetch and Dispatch Unit (PDU), it controls the Integer Core Register File (ICRF), and it routes valid data to each integer functional unit. The G Stage sends up to two floating-point or graphics instructions out of the four candidates to the Floating-Point and Graphics Unit (FGU). The G Stage logic is responsible for comparing register addresses for integer data bypassing and for handling pipeline stalls due to interlocks.

# 2.2.4 Stage 4: Execution (E) Stage

Data from the integer register file is processed by the two integer ALUs during this cycle (if the instruction group includes ALU operations). Results are computed and are available for other instructions (through bypasses) in the very next cycle. The virtual address of a memory operation is also calculated during the E Stage, in parallel with ALU computation.

FLOATING-POINT AND GRAPHICS UNIT: The Register (R) Stage of the FGU. The floating-point register file is accessed during this cycle. The instructions are also further decoded and the FGU control unit selects the proper bypasses for the current instructions.

# 2.2.5 Stage 5: Cache Access (C) Stage

The virtual address of memory operations calculated in the E Stage is sent to the tag RAM to determine if the access (load or store type) is a hit or a miss in the D-Cache. In parallel the virtual address is sent to the data MMU to be translated into a physical address. On a load when there are no other outstanding loads, the data array is accessed so that the data can be forwarded to dependent instructions in the pipeline as soon as possible.

ALU operations executed in the E Stage generate condition codes in the C Stage. The condition codes are sent to the PDU, which checks whether a conditional branch in the group was correctly predicted. If the branch was mispredicted, earlier instructions in the pipe are flushed and the correct instructions are fetched. The results of ALU operations are not modified after the E Stage; the data merely propagates down the pipeline (through the annex register file), where it is available for bypassing for subsequent operations.

FLOATING-POINT AND GRAPHICS UNIT: The  $X_1$  Stage of the FGU. Floating-point and graphics instructions start their execution during this stage. Instructions of latency one also finish their execution phase during the  $X_1$  Stage.

# 2.2.6 Stage 6: N<sub>1</sub> Stage

A data cache miss/hit or a TLB miss/hit is determined during the  $N_1$  Stage. If a load misses the D-Cache, it enters the Load Buffer. The access will arbitrate for the E-Cache if there are no older unissued loads. If a TLB miss is detected, a trap will be taken and the address translation is obtained through a software routine.

The physical address of a store is sent to the Store Buffer during this stage. To avoid pipeline stalls when store data is not immediately available, the store address and data parts are decoupled and sent to the Store Buffer separately.

FLOATING-POINT AND GRAPHICS UNIT: The  $X_2$  stage of the FGU. Execution continues for most operations.

# 2.2.7 Stage 7: N<sub>2</sub> Stage

Most floating-point instructions finish their execution during this stage. After  $N_2$ , data can be bypassed to other stages or forwarded to the data portion of the Store Buffer. All loads that have entered the Load Buffer in  $N_1$  continue their progress through the buffer; they will reappear in the pipeline only when the data comes back. Normal dependency checking is performed on all loads, including those in the load buffer.

FLOATING-POINT AND GRAPHICS UNIT: The X<sub>3</sub> stage of the FGU.

# 2.2.8 Stage 8: N<sub>3</sub> Stage

UltraSPARC resolves traps at this stage.

# 2.2.9 Stage 9: Write (W) Stage

All results are written to the register files (integer and floating-point) during this stage. All actions performed during this stage are irreversible. After this stage, instructions are considered terminated.

UltraSPARC User's Manual

# 3.1 Introduction

#### 3.1.1 Level-1 Caches

UltraSPARC's Level-1 D-Cache is virtually indexed, physically tagged (VIPT). Virtual addresses are used to index into the D-Cache tag and data arrays while accessing the D-MMU (that is, the dTLB). The resulting tag is compared against the translated physical address to determine D-Cache hits.

A side-effect inherent in a virtual-indexed cache is *address aliasing*; this issue is addressed in Section 5.2.1, "Address Aliasing Flushing," on page 28.

UltraSPARC's Level-1 I-Cache is physically indexed, physically tagged (PIPT). The lowest 13 bits of instruction addresses are used to index into the I-Cache tag and data arrays while accessing the I-MMU (that is, the iTLB). The resulting tag is compared against the translated physical address to determine I-Cache hits.

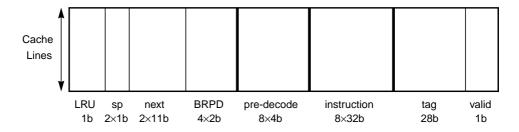

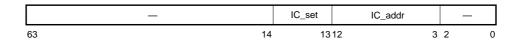

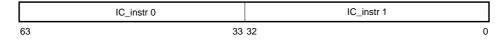

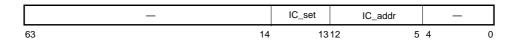

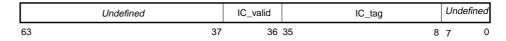

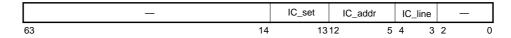

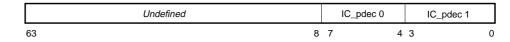

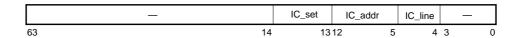

### 3.1.1.1 Instruction Cache (I-Cache)

The I-Cache is a 16 Kb pseudo-two-way set-associative cache with 32-byte blocks. The set is predicted based on the next fetch address; thus, only the index bits of an address are necessary to address the cache (that is, the lowest 13 bits, which matches the minimum page size of 8Kb). Instruction fetches bypass the instruction cache under the following conditions:

- When the I-Cache enable or I-MMU enable bits in the LSU\_Control\_Register are clear (see Section A.6, "LSU\_Control\_Register," on page 306)

- When the processor is in RED\_state, or

• When the I-MMU maps the fetch as noncacheable.

The instruction cache snoops stores from other processors or DMA transfers, but it is not updated by stores in the same processor, except for block commit stores (see Section 13.6.4, "Block Load and Store Instructions," on page 230). The FLUSH instruction can be used to maintain coherency. Block commit stores update the I-Cache but do not flush instructions that have already been prefetched into the pipeline. A FLUSH, DONE, or RETRY instruction can be used to flush the pipeline. For block copies that must maintain I-Cache coherency, it is more efficient to use block commit stores in the loop, followed by a single FLUSH instruction to flush the pipeline.

**Note:** The size of each I-Cache set is the same as the page size in UltraSPARC-I and UltraSPARC-II; thus, the virtual index bits equal the physical index bits.

# 3.1.1.2 Data Cache (D-Cache)

The D-Cache is a write-through, nonallocating-on-write-miss 16-Kb direct mapped cache with two 16-byte sub-blocks per line. Data accesses bypass the data cache when the D-Cache enable bit in the LSU\_Control\_Register is clear (see Section A.6, "LSU\_Control\_Register," on page 306). Load misses will not allocate in the D-Cache if the D-MMU enable bit in the LSU\_Control\_Register is clear or the access is mapped by the D-MMU as virtual noncacheable.

**Note:** A noncacheable access may access data in the D-Cache from an earlier cacheable access to the same physical block, unless the D-Cache is disabled. Software must flush the D-Cache when changing a physical page from cacheable to noncacheable (see Section 5.2, "Cache Flushing").

# 3.1.2 Level-2 PIPT External Cache (E-Cache)

UltraSPARC's level-2 (external) cache (the E-Cache) is physically indexed, physically tagged (PIPT). This cache has no references to virtual address and context information. The operating system needs no knowledge of such caches after initialization, except for stable storage management and error handling.

Memory accesses must be cacheable in the E-Cache to allow use of UltraSPARC's ECC checking. As a result, there is no E-Cache enable bit in the LSU\_Control\_Register.

Instruction fetches bypass the E-Cache when:

- The I-MMU is disabled, or

- The processor is in RED\_state, or

- The access is mapped by the I-MMU as physically noncacheable

Data accesses bypass the E-Cache when:

- The D-MMU enable bit (DM) in the LSU\_Control\_Register is clear, or

- The access is mapped by the D-MMU as nonphysical cacheable (unless ASI\_PHYS\_USE\_EC is used).

The system must provide a noncacheable, ECC-less scratch memory for use of the booting code until the MMUs are enabled.

The E-Cache is a unified, write-back, allocating, direct-mapped cache. The E-Cache always includes the contents of the I-Cache and D-Cache. The E-Cache size is model dependent (see Table 1-5 on page 10); its line size is 64 bytes.

Block loads and block stores, which load or store a 64-byte line of data from memory to the floating-point register file, do not allocate into the E-Cache, in order to avoid pollution.

UltraSPARC User's Manual

#### 4.1 Introduction

This chapter describes the UltraSPARC Memory Management Unit as it is seen by the operating system software. The UltraSPARC MMU conforms to the requirements set forth in *The SPARC Architecture Manual. Version 9.*

**Note:** The UltraSPARC MMU does not conform to the SPARC-V8 Reference MMU Specification. In particular, the UltraSPARC MMU supports a 44-bit virtual address space, software TLB miss processing only (no hardware page table walk), simplified protection encoding, and multiple page sizes. All of these differ from features required of SPARC-V8 Reference MMUs.

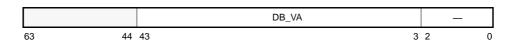

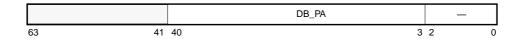

### 4.2 Virtual Address Translation

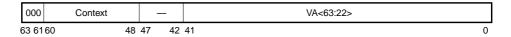

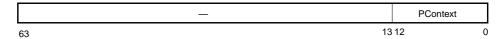

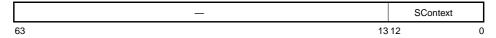

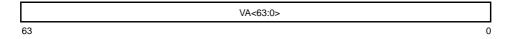

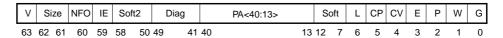

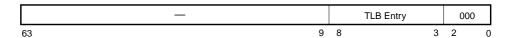

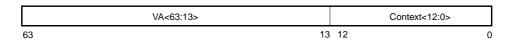

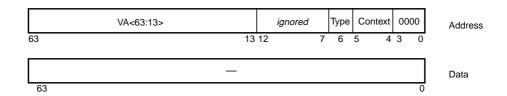

The UltraSPARC MMU supports four page sizes: 8 Kb, 64 Kb, 512 Kb, and 4 Mb. It supports a 44-bit virtual address space, with 41 bits of physical address. During each processor cycle the UltraSPARC MMU provides one instruction and one data virtual-to-physical address translation. In each translation, the virtual page number is replaced by a physical page number, which is concatenated with the page offset to form the full physical address, as illustrated in Figure 4-1 on page 22. (This figure shows the full 64-bit virtual address, even though UltraSPARC supports only 44 bits of VA.)

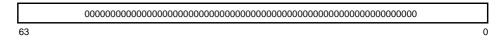

Figure 4-1 Virtual-to-physical Address Translation for all Page Sizes

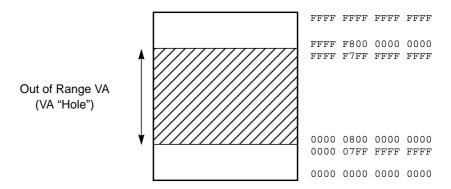

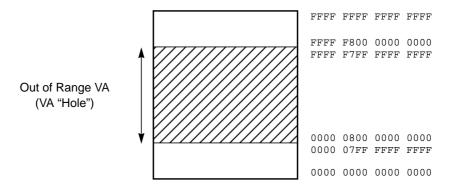

UltraSPARC implements a 44-bit virtual address space in two equal halves at the extreme lower and upper portions of the full 64-bit virtual address space. Virtual addresses between 0000 0800 0000 0000 $_{16}$  and FFFF F7FF FFFF FFFF $_{16}$ , inclusive, are termed "out of range" for UltraSPARC and are illegal. (In other words, virtual address bits VA<63:43> must be either all zeros or all ones.) Figure 4-2 on page 23 illustrates the UltraSPARC virtual address space.

Figure 4-2 UltraSPARC's 44-bit Virtual Address Space, with Hole (Same as Figure 14-2)

**Note:** Throughout this document, when virtual address fields are specified as 64-bit quantities, they are assumed to be sign-extended based on VA<43>.

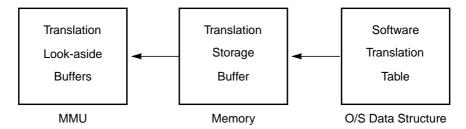

The operating system maintains translation information in a data structure called the Software Translation Table. The I- and D-MMU each contain a hardware Translation Lookaside Buffer (iTLB and dTLB); these act as independent caches of the Software Translation Table, providing one-cycle translation for the more frequently accessed virtual pages.

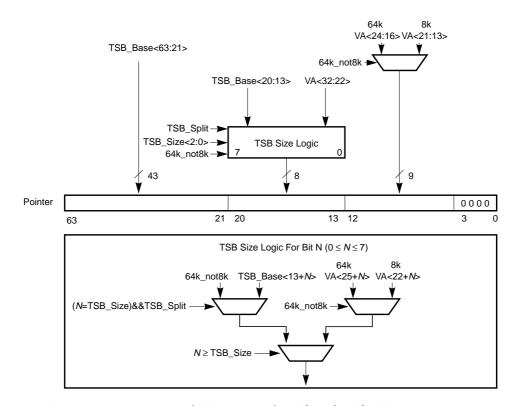

Figure 4-3 on page 24 shows a general software view of the UltraSPARC MMU. The TLBs, which are part of the MMU hardware, are small and fast. The Software Translation Table, which is kept in memory, is likely to be large and complex. The Translation Storage Buffer (TSB), which acts like a direct-mapped cache, is the interface between the two. The TSB can be shared by all processes running on a processor, or it can be process specific. The hardware does not require any particular scheme.

The term "TLB hit" means that the desired translation is present in the MMU's on-chip TLB. The term "TLB miss" means that the desired translation is not present in the MMU's on-chip TLB. On a TLB miss the MMU immediately traps to software for TLB miss processing. The TLB miss handler has the option of filling the TLB by any means available, but it is likely to take advantage of the TLB miss support features provided by the MMU, since the TLB miss handler is time critical code. Hardware support is described in Section 6.3.1, "Hardware Support for TSB Access," on page 45.

Figure 4-3 Software View of the UltraSPARC MMU

Aliasing between pages of different size (when multiple VAs map to the same PA) may take place, as with the SPARC-V8 Reference MMU. The reverse case, when multiple mappings from one VA/context to multiple PAs produce a multiple TLB match, is not detected in hardware; it produces undefined results.

**Note:** The hardware ensures the physical reliability of the TLB on multiple matches.

# Section II — Going Deeper

| •••• | 27 |

|------|----|

| •••• | 41 |

|      |    |

| 5.  | Cache and Memory Interactions         | 27  |

|-----|---------------------------------------|-----|

| 6.  | MMU Internal Architecture             | 41  |

| 7.  | UltraSPARC External Interfaces        | 73  |

| 8.  | Address Spaces, ASIs, ASRs, and Traps | 145 |

| 9.  | Interrupt Handling                    | 161 |

| 10. | Reset and RED_state                   | 169 |

| 11  | Error Handling                        | 175 |

UltraSPARC User's Manual

#### 5.1 Introduction

This chapter describes various interactions between the caches and memory, and the management processes that an operating system must perform to maintain data integrity in these cases. In particular, it discusses:

- When and how to invalidate one or more cache entries

- The differences between cacheable and non-cacheable accesses

- The ordering and synchronization of memory accesses

- Accesses to addresses that cause side effects (I/O accesses)

- Non-faulting loads

- Instruction prefetching

- Load and store buffers

This chapter only address coherence in a uniprocessor environment. For more information about coherence in multi-processor environments, see Chapter 15, "SPARC-V9 Memory Models."

### 5.2 Cache Flushing

Data in the level-1 (read-only or write-through) caches can be flushed by invalidating the entry in the cache. Modified data in the level-2 (writeback) cache must be written back to memory when flushed.

Cache flushing is required in the following cases:

#### I-Cache:

Flush is needed before executing code that is modified by a local store instruction other than block commit store, see Section 3.1.1.1, "Instruction Cache (I-Cache)." This is done with the FLUSH instruction or using ASI accesses. See Section A.7, "I-Cache Diagnostic Accesses," on page 309. When ASI accesses are used, software must ensure that the flush is done on the same processor as the stores that modified the code space.

#### D-Cache:

Flush is needed when a physical page is changed from (virtually) cacheable to (virtually) noncacheable, or when an illegal address alias is created (see Section 5.2.1, "Address Aliasing Flushing," on page 28). This is done with a displacement flush (see Section 5.2.3, "Displacement Flushing," on page 29) or using ASI accesses. See Section A.8, "D-Cache Diagnostic Accesses," on page 314.

#### E-Cache:

Flush is needed for stable storage. Examples of stable storage include battery-backed memory and transaction logs. This is done with either a displacement flush (see Section 5.2.3, "Displacement Flushing," on page 29) or a store with ASI\_BLK\_COMMIT\_{PRIMARY,SECONDARY}. Flushing the E-Cache will flush the corresponding blocks from the I- and D-Caches, because UltraSPARC maintains inclusion between the external and internal caches. See Section 5.2.2, "Committing Block Store Flushing," on page 29.

### 5.2.1 Address Aliasing Flushing

A side-effect inherent in a virtual-indexed cache is *illegal address aliasing*. Aliasing occurs when multiple virtual addresses map to the same physical address. Since UltraSPARC's D-Cache is indexed with the virtual address bits and is larger than the minimum page size, it is possible for the different aliased virtual addresses to end up in different cache blocks. Such aliases are illegal because updates to one cache block will not be reflected in aliased cache blocks.

Normally, software avoids illegal aliasing by forcing aliases to have the same address bits (*virtual color*) up to an *alias boundary*. For UltraSPARC, the minimum alias boundary is 16Kb; this size may increase in future designs. When the alias boundary is violated, software must flush the D-Cache if the page was virtual cacheable. In this case, only one mapping of the physical page can be allowed in the D-MMU at a time. Alternatively, software can turn off virtual caching of illegally aliased pages. This allows multiple mappings of the alias to be in the D-MMU and avoids flushing the D-Cache each time a different mapping is referenced.

**Note:** A change in virtual color when allocating a free page does not require a D-Cache flush, because the D-Cache is write-through.

### 5.2.2 Committing Block Store Flushing

In UltraSPARC, stable storage must be implemented by software cache flush. Data that is present and modified in the E-Cache must be written back to the stable storage.

UltraSPARC implements two ASIs (ASI\_BLK\_COMMIT\_{PRIMARY,SECOND-ARY}) to perform these writebacks efficiently when software can ensure exclusive write access to the block being flushed. Using these ASIs, software can write back data from the floating-point registers to memory and invalidate the entry in the cache. The data in the floating-point registers must first be loaded by a block load instruction. A MEMBAR #Sync instruction is needed to ensure that the flush is complete. See also Section 13.6.4, "Block Load and Store Instructions," on page 230.

### 5.2.3 Displacement Flushing

Cache flushing also can be accomplished by a displacement flush. This is done by reading a range of read-only addresses that map to the corresponding cache line being flushed, forcing out modified entries in the local cache. Care must be taken to ensure that the range of read-only addresses is mapped in the MMU before starting a displacement flush, otherwise the TLB miss handler may put new data into the caches.

**Note:** Diagnostic ASI accesses to the E-Cache can be used to invalidate a line, but they are generally not an alternative to displacement flushing. Modified data in the E-Cache will not be written back to memory using these ASI accesses. See Section A.9, "E-Cache Diagnostics Accesses," on page 315.

# 5.3 Memory Accesses and Cacheability

**Note:** Atomic load-store instructions are treated as both a load and a store; they can be performed only in cacheable address spaces.

#### 5.3.1 Coherence Domains

Two types of memory operations are supported in UltraSPARC: cacheable and noncacheable accesses, as indicated by the page translation. Cacheable accesses are inside the coherence domain; noncacheable accesses are outside the coherence domain.

SPARC-V9 does not specify memory ordering between cacheable and noncacheable accesses. In TSO mode, UltraSPARC maintains TSO ordering, regardless of the cacheability of the accesses. For SPARC-V9 compatibility while in PSO or RMO mode, a MEMBAR #Lookaside should be used between a store and a subsequent load to the same noncacheable address. See Section 8, "Memory Models," in *The SPARC Architecture Manual, Version 9* for more information about the SPARC-V9 memory models.

**Note:** On UltraSPARC, a MEMBAR #Lookaside executes more efficiently than a MEMBAR #StoreLoad.

#### 5.3.1.1 Cacheable Accesses

Accesses that fall within the coherence domain are called cacheable accesses. They are implemented in UltraSPARC with the following properties:

- Data resides in real memory locations.

- They observe supported cache coherence protocol(s).

- The unit of coherence is 64 bytes.

#### 5.3.1.2 Non-Cacheable and Side-Effect Accesses

Accesses that are outside the coherence domain are called noncacheable accesses. Some of these memory (-mapped) locations may have side-effects when accessed. They are implemented in UltraSPARC with the following properties:

- Data may or may not reside in real memory locations.

- Accesses may result in program-visible side-effects; for example, memory-mapped I/O control registers in a UART may change state when read.

- They may not observe supported cache coherence protocol(s).

- The smallest unit in each transaction is a single byte.

Noncacheable accesses with the E-bit set (that is, those having side-effects) are all strongly ordered with respect to other noncacheable accesses with the E-bit set. In addition, store buffer compression is disabled for these accesses. Speculative loads with the E-bit set cause a <code>data\_access\_exception</code> trap (with SFSR.FT=2, speculative load to page marked with E-bit).

**Note:** The side-effect attribute does not imply noncacheability.

### 5.3.1.3 Global Visibility and Memory Ordering

A memory access is considered globally visible when it has been acknowledged by the system. In order to ensure the correct ordering between the cacheable and noncacheable domains, explicit memory synchronization is needed in the form of MEMBARs or atomic instructions. Code Example 5-1 illustrates the issues involved in mixing cacheable and noncacheable accesses.

#### Code Example 5-1 Memory Ordering and MEMBAR Examples

```

Assume that all accesses go to non-side-effect memory locations.

Process A:

While (1)

Store D1:data produced

MEMBAR #StoreStore (needed in PSO, RMO)

Store F1:set flag

While F1 is set (spin on flag)

Load F1

MEMBAR #LoadLoad | #LoadStore (needed in RMO)

Load D2

Process B:

While (1)

While F1 is cleared (spin on flag)

Load F1

MEMBAR #LoadLoad | #LoadStore (needed in RMO)

Load D1

Store D2

MEMBAR #StoreStore (needed in PSO, RMO)

Store F1:clear flag

}

```

**Note:** A MEMBAR #MemIssue or MEMBAR #Sync is needed if ordering of cacheable accesses following noncacheable accesses must be maintained in PSO or RMO.

Due to load and store buffers implemented in UltraSPARC, the above example may not work in PSO and RMO modes without the MEMBARs shown in the program segment.

In TSO mode, loads and stores (except block stores) cannot pass earlier loads, and stores cannot pass earlier stores; therefore, no MEMBAR is needed.

In PSO mode, loads are completed in program order, but stores are allowed to pass earlier stores; therefore, only the MEMBAR at #1 is needed between updating data and the flag.

In RMO mode, there is no implicit ordering between memory accesses; therefore, the MEMBARs at both #1 and #2 are needed.

### 5.3.2 Memory Synchronization: MEMBAR and FLUSH

The MEMBAR (STBAR in SPARC-V8) and FLUSH instructions are provide for explicit control of memory ordering in program execution. MEMBAR has several variations; their implementations in UltraSPARC are described below. See Section A.31, "Memory Barrier," Section 8.4.3, "The MEMBAR Instruction," and Section J, "Programming With the Memory Models," in *The SPARC Architecture Manual*, *Version 9* for more information.

### 5.3.2.1 MEMBAR #LoadLoad

Forces all loads after the MEMBAR to wait until all loads before the MEMBAR have reached global visibility.

### 5.3.2.2 MEMBAR #StoreLoad

Forces all loads after the MEMBAR to wait until all stores before the MEMBAR have reached global visibility.

### 5.3.2.3 MEMBAR #LoadStore

Forces all stores after the MEMBAR to wait until all loads before the MEMBAR have reached global visibility.

### 5.3.2.4 MEMBAR #StoreStore and STBAR

Forces all stores after the MEMBAR to wait until all stores before the MEMBAR have reached global visibility.

**Note:** STBAR has the same semantics as MEMBAR #StoreStore; it is included for SPARC-V8 compatibility.

**Note:** The above four MEMBARs do not guarantee ordering between cacheable accesses after noncacheable accesses.

#### 5.3.2.5 MEMBAR #Lookaside

SPARC-V9 provides this variation for implementations having virtually tagged store buffers that do not contain information for snooping.

**Note:** For SPARC-V9 compatibility, this variation should be used before issuing a load to an address space that cannot be snooped.

#### 5.3.2.6 MEMBAR #MemIssue

Forces all outstanding memory accesses to be *completed* before any memory access instruction after the MEMBAR is issued. It must be used to guarantee ordering of cacheable accesses following non-cacheable accesses. For example, I/O accesses must be followed by a MEMBAR #MemIssue before subsequent cacheable stores; this ensures that the I/O accesses reach global visibility before the cacheable stores after the MEMBAR.

Note: MEMBAR #MemIssue is different from the combination of MEMBAR #LoadLoad | #LoadStore | #StoreLoad | #StoreStore. MEMBAR #MemIssue orders cacheable and noncacheable domains; it prevents memory accesses after it from issuing until it completes.

### 5.3.2.7 MEMBAR #Sync (Issue Barrier)

Forces all outstanding instructions and all deferred errors to be completed before any instructions after the MEMBAR are issued.

**Note:** MEMBAR #Sync is a costly instruction; unnecessary usage may result in substantial performance degradation.

### 5.3.2.8 Self-Modifying Code (FLUSH)

The SPARC-V9 instruction set architecture does not guarantee consistency between code and data spaces. A problem arises when code space is dynamically modified by a program writing to memory locations containing instructions. LISP programs and dynamic linking require this behavior. SPARC-V9 provides the FLUSH instruction to synchronize instruction and data memory after code space has been modified.

In UltraSPARC, a FLUSH behaves like a store instruction for the purpose of memory ordering. In addition, all instruction (pre-)fetch buffers are invalidated. The issue of the FLUSH instruction is delayed until previous (cacheable) stores are completed. Instruction (pre-)fetch resumes at the instruction immediately after the FLUSH.

### 5.3.3 Atomic Operations

SPARC-V9 provides three atomic instructions to support mutual exclusion. These instructions behave like both a load and a store, but the operations are carried out indivisibly. Atomic instructions may be used only in the cacheable domain.

An atomic access with a restricted ASI in unprivileged mode (PSTATE.PRIV=0) causes a *privileged\_action* trap. An atomic access with a noncacheable address causes a *data\_access\_exception* trap (with SFSR.FT=4, atomic to page marked noncacheable). An atomic access with an unsupported ASI causes a *data\_access\_exception* trap (with SFSR.FT=8, illegal ASI value or virtual address). Table 5-1 lists the ASIs that support atomic accesses.

Unrestricted

Unrestricted

Unrestricted

| ASI Name                          | Access     |

|-----------------------------------|------------|

| ASI_NUCLEUS{_LITTLE}              | Restricted |

| ASI_AS_IF_USER_PRIMARY{_LITTLE}   | Restricted |

| ASI_AS_IF_USER_SECONDARY{_LITTLE} | Restricted |

Table 5-1 ASIs that Support SWAP, LDSTUB, and CAS

ASI\_PRIMARY{\_LITTLE}

ASI\_SECONDARY{\_LITTLE}

ASI\_PHYS\_USE\_EC{\_LITTLE}

**Note:** Atomic accesses with non-faulting ASIs are not allowed, because these ASIs have the load-only attribute.

#### 5.3.3.1 SWAP Instruction

SWAP atomically exchanges the lower 32 bits in an integer register with a word in memory. This instruction is issued only after store buffers are empty. Subsequent loads interlock on earlier SWAPs. A cache miss will allocate the corresponding line.

**Note:** If a page is marked as virtually-non-cacheable but physically cacheable, allocation is done to the E-Cache only.

#### 5.3.3.2 LDSTUB Instruction

LDSTUB behaves like SWAP, except that it loads a byte from memory into an integer register and atomically writes all ones (FF<sub>16</sub>) into the addressed byte.

# 5.3.3.3 Compare and Swap (CASX) Instruction

Compare-and-swap combines a load, compare, and store into a single atomic instruction. It compares the value in an integer register to a value in memory; if they are equal, the value in memory is swapped with the contents of a second integer register. All of these operations are carried out atomically; in other words, no other memory operation may be applied to the addressed memory location until the entire compare-and-swap sequence is completed.

# 5.3.4 Non-Faulting Load

A non-faulting load behaves like a normal load, except that:

- It does not allow side-effect access. An access with the E-bit set causes a data\_access\_exception trap (with SFSR.FT=2, Speculative Load to page marked E-bit).

- It can be applied to a page with the NFO-bit set; other types of accesses will cause a *data\_access\_exception* trap (with SFSR.FT=10<sub>16</sub>, Normal access to page marked NFO).

Non-faulting loads are issued with ASI\_PRIMARY\_NO\_FAULT{\_LITTLE}, or ASI\_SECONDARY\_NO\_FAULT{\_LITTLE}. A store with a NO\_FAULT ASI causes a *data\_access\_exception* trap (with SFSR.FT=8, Illegal RW).

When a non-faulting load encounters a TLB miss, the operating system should attempt to translate the page. If the translation results in an error (for example, address out of range), a 0 is returned and the load completes silently.

Typically, optimizers use non-faulting loads to move loads before conditional control structures that guard their use. This technique potentially increases the distance between a load of data and the first use of that data, in order to hide latency; it allows for more flexibility in code scheduling. It also allows for improved performance in certain algorithms by removing address checking from the critical code path.

For example, when following a linked list, non-faulting loads allow the null pointer to be accessed safely in a read-ahead fashion if the OS can ensure that the page at virtual address  $0_{16}$  is accessed with no penalty. The NFO (non-fault access only) bit in the MMU marks pages that are mapped for safe access by non-faulting loads, but can still cause a trap by other, normal accesses. This allows programmers to trap on wild pointer references (many programmers count on an exception being generated when accessing address  $0_{16}$  to debug code) while benefitting from the acceleration of non-faulting access in debugged library routines.

### 5.3.5 PREFETCH Instructions

Table 5-2 shows which UltraSPARC models support the PREFETCH{A} instructions.

Table 5-2 PREFETCH{A} Instruction Support

|             | UltraSPARC-I | UltraSPARC-II |

|-------------|--------------|---------------|

| PREFETCH{A} |              | ✓             |

UltraSPARC models that do not support PREFETCH treat it as a NOP.

#### 5.3.5.1 PREFETCH Behavior and Limitations

UltraSPARC processors that do support PREFETCH behave in the following ways:

All PREFETCH instructions are enqueued on the load buffer, except as noted below.

- Some conditions, noted below, cause an otherwise supported PREFETCH to be treated as a NOP and removed from the load buffer when it reaches the front of the queue.

- No PREFETCH will cause a trap except:

- PREFETCH with fcn=5..15 causes an illegal\_instruction trap, as defined in The SPARC Architecture Manual, Version 9.

- Watchpoint, as defined in Section A.5, "Watchpoint Support," on page 304.

- Any PREFETCHA that specifies an internal ASI in the following ranges is not enqueued on the load buffer and is not executed:

- $40_{16}..4F_{16}$ ,  $50_{16}..5F_{16}$ ,  $60_{16}..6F_{16}$ ,  $76_{16}$ ,  $77_{16}$

- The following conditions cause a PREFETCH{A} to be treated as a NOP:

- PREFECTH with fcn=16..31, as defined in The SPARC Architecture Manual, Version 9.

- A data\_access\_MMU\_miss exception

- D-MMU disabled

- For PREFETCHA, any ASI other than the following  $04_{16}$ ,  $0C_{16}$ ,  $10_{16}$ ,  $11_{16}$ ,  $18_{16}$ ,  $19_{16}$ ,  $80_{16}$ ... $83_{16}$ ,  $88_{16}$ ... $8B_{16}$

- Attempt to PREFETCH to a noncacheable page

- Alignment is not checked on PREFETCH{A}. The 5 least significant address are ignored.

### 5.3.5.2 Implemented fcn Values

Table 5-3 lists the supported values for *fcn* and their meanings.

*Table 5-3* PREFETCH{A} Variants

| fcn  | Prefetch Function           |

|------|-----------------------------|

| 0    | Prefetch for several reads  |

| 1    | Prefetch for one read       |

| 2    | Prefetch page               |

| 3    | Prefetch for several writes |

| 4    | Prefetch for one write      |

| 515  | illegal_instruction trap    |

| 1631 | NOP                         |

For more information, including an enumeration of the bus transaction the each *fcn* value causes, see Section 14.4.5, "PREFETCH{A} (Impdep #103, 117)," on page 248.

#### 5.3.6 Block Loads and Stores

Block load and store instructions work like normal floating-point load and store instructions, except that the data size (granularity) is 64 bytes per transfer. See Section 13.6.4, "Block Load and Store Instructions," on page 230 for a full description of the instructions.

#### 5.3.7 I/O and Accesses with Side-effects

I/O locations may not behave with memory semantics. Loads and stores may have side-effects; for example, a read access may clear a register or pop an entry off a FIFO. A write access may set a register address port so that the next access to that address will read or write a particular internal registers, etc. Such devices are considered order sensitive. Also, such devices may only allow accesses of a fixed size, so store buffer merging of adjacent stores or stores within a 16-byte region will cause an access error.

The UltraSPARC MMU includes an attribute bit (the E-Bit) in each page translation, which, when set, indicates that access to this page cause side effects. Accesses other than block loads or stores to pages that have this bit set have the following behavior:

- Noncacheable accesses are strongly ordered with respect to each other

- Noncacheable loads with the E-bit set will not be issued until all previous control transfers (including exceptions) are resolved.

- Store buffer compression is disabled for noncacheable accesses.

- Non-faulting loads are not allowed and will cause a *data\_access\_exception* trap (with SFSR.FT = 2, speculative load to page marked E-bit).

- A MEMBAR may be needed between side-effect and non-side-effect accesses while in PSO and RMO modes.

#### 5.3.8 Instruction Prefetch to Side-Effect Locations

UltraSPARC does instruction prefetching and follows branches that it predicts will be taken. Addresses mapped by the I-MMU may be accessed even though they are not actually executed by the program. Normally, locations with side effects or those that generate time-outs or bus errors will not be mapped by the I-MMU, so prefetching will not cause problems. When running with the I-MMU disabled, however, software must avoid placing data in the path of a control transfer instruction target or sequentially following a trap or conditional branch instruction. Data can be placed sequentially following the delay slot of a BA(,pt),

CALL, or JMPL instruction. Instructions should not be placed within 256 bytes of locations with side effects. See Section 16.2.10, "Return Address Stack (RAS)," on page 272 for other information about JMPLs and RETURNs.

### 5.3.9 Instruction Prefetch When Exiting RED\_state

Exiting RED\_state by writing 0 to PSTATE.RED in the delay slot of a JMPL is not recommended. A noncacheable instruction prefetch may be made to the JMPL target, which may be in a cacheable memory area. This may result in a bus error on some systems, which will cause an <code>instruction\_access\_error</code> trap. The trap can be masked by setting the NCEEN bit in the ESTATE\_ERR\_EN register to zero, but this will mask all non-correctable error checking. To avoid this problem exit RED\_state with DONE or RETRY, or with a JMPL to a noncacheable target address.

#### 5.3.10 UltraSPARC Internal ASIs

ASIs in the ranges  $46_{16}..6F_{16}$  and  $76_{16}..7F_{16}$  are used for accessing internal UltraSPARC states. Stores to these ASIs do not follow the normal memory model ordering rules. Correct operation requires the following:

- A MEMBAR #Sync is needed after an internal ASI store other than MMU

ASIs before the point that side effects must be visible. This MEMBAR must

precede the next load or noninternal store. The MEMBAR also must be in or

before the delay slot of a delayed control transfer instruction of any type. This

is necessary to avoid corrupting data.

- A FLUSH, DONE, or RETRY is needed after an internal store to the MMU ASIs (ASI 50<sub>16</sub>..52<sub>16</sub>, 54<sub>16</sub>..5F<sub>16</sub>) or to the IC bit in the LSU control register before the point that side effects must be visible. Stores to D-MMU registers other than the context ASIs may also use a MEMBAR #Sync. One of these instructions must precede the next load or noninternal store. They also must be in or before the delay slot of a delayed control transfer instruction. This is necessary to avoid corrupting data.

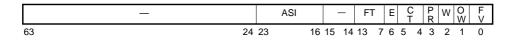

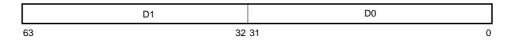

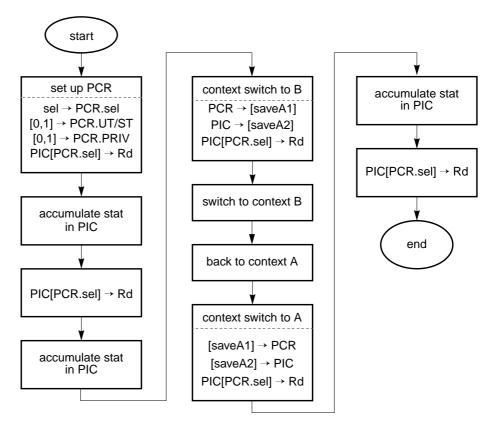

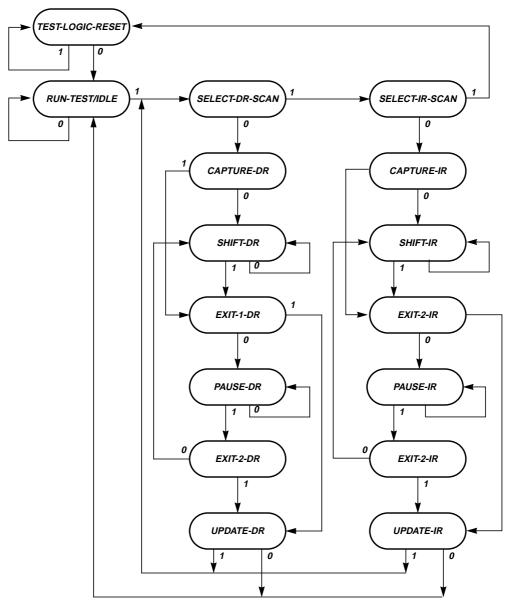

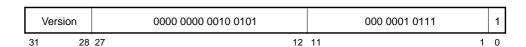

### 5.4 Load Buffer